- Lattice lse vs synplify pro how to#

- Lattice lse vs synplify pro pro#

- Lattice lse vs synplify pro code#

One other interesting thing I learned in the process was that the HFOSC block uses a global buffer, but the Lattice tool doesn't recognize that up front so it can run into issues during post-synthesis P&R.There are some reported issues with the website, although I've never experienced any. Take note of the pin names - they are different from the Lattice guides which is why I was having issues instantiating the component. In your instance instantiations: u_osc : SB_HFOSC In your component definitions: component SB_HFOSC The proper process for instantiating a lattice HFOSC IP block is as follows: I was able to resolve this issue through Lattice's customer support portal.

Lattice lse vs synplify pro how to#

The docs claim its there, but I cant find any clear docs how to use it, at least not for iCE40UL.

Lattice lse vs synplify pro code#

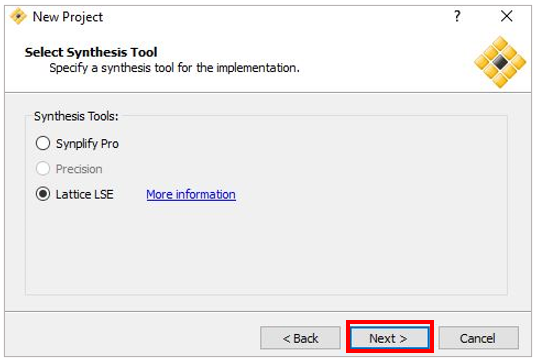

I simply don't understand how to reset one-hot code state machines without an internal system level global set/reset available. To the top, but I had severe issues with resetting state machines, so I gave up on it. Now you can add work library to the top of your code and instantiate like normal: library work Īlternatively, using the onboard "Synplify Pro" synthesis tool, I had some success if I added library sb_ice40_components_syn Not doing this will fail P&R, but will pass synthesis. Fix the bug in it edit the attribute ROUTE_THROUGH_FABRIC to use string type instead of boolean, and "1"/"0" instead of true/false where it is used. Add this file to your project: \LSE\userware\NT\SYNTHESIS_HEADERS\sb_ice40_components_syn.vhd There is a VHDL package file containing them, but I find bugs in it. This is due to components defined in VERILOG and VHDL doesn't see those at synth stage unless you define the components manually in VHDL. ICEcube2 (200) obviously isn't ready to VHDL out of the package with the "Lattice LSE Synthesis" tool.

Lattice lse vs synplify pro pro#

I tried compiling using the built-in ICECube2 compiler as well as Synplify Pro but receive similar errors in each case.Īm I following the correct process to implement the HFOSC in my code? Do I need to download additional libraries that aren't automatically provided in the ICECube2 suite? As you can see in the code above, I have included the IEEE Vital libraries. When I try to synthesize the code, I receive a slew of errors, all of which appear to be related to "vitaldelaytype01" and "vital_level0" not being defined. I also added the component definition (to my top architecture) from vcomponent_vital.vhd: component SB_HFOSC is Paths => (-0 =>(CLKHFEN_ipd'last_event, tpd_CLKHFEN_CLKHF, true),Ġ =>(CLKHFPU_ipd'last_event, tpd_CLKHFPU_CLKHF, true)), Variable CLKHF_GlitchData : VitalGlitchDataType VITALPathDelay :process (CLKHFEN_ipd,CLKHF_sig,CLKHFPU_ipd) VitalWireDelay (CLKHFPU_ipd, CLKHFPU, tipd_CLKHFPU)

VitalWireDelay (CLKHFEN_ipd, CLKHFEN, tipd_CLKHFEN) I added a new file in my project which contains the following code from sb_ice_syn_vital.vhd:. Then I found this article: lattice FPGA internal oscillator simulation issues which mentions adding lattice components to your project file. When I tried this, I received errors related to the component SB_HFOSC not being defined. The code base I'm working from is in VHDL, so I've added the component to my architecture as follows: SB_HFOSC : OscInst0 Per the iCE40 Oscillator Usage Guide Appendix, the code in verilog should look like this: SB_HFOSC OSCInst0 ( I'm having trouble using the internal oscillator for the Lattice ICE5LP4K.

0 kommentar(er)

0 kommentar(er)